2D secure circuit

Logic locking implemented by 2D reconfigurable BP FETs

Security has become a major concern for modern integrated circuit (IC) design. With the development of reverse engineering techniques based on high-resolution imaging methods such as X-ray imaging and transmission electron microscopy (TEM), malicious attackers can retrieve the layout of an IC chip, and thus steal the intellectual properties or exploit hardware vulnerabilities in the chip design.

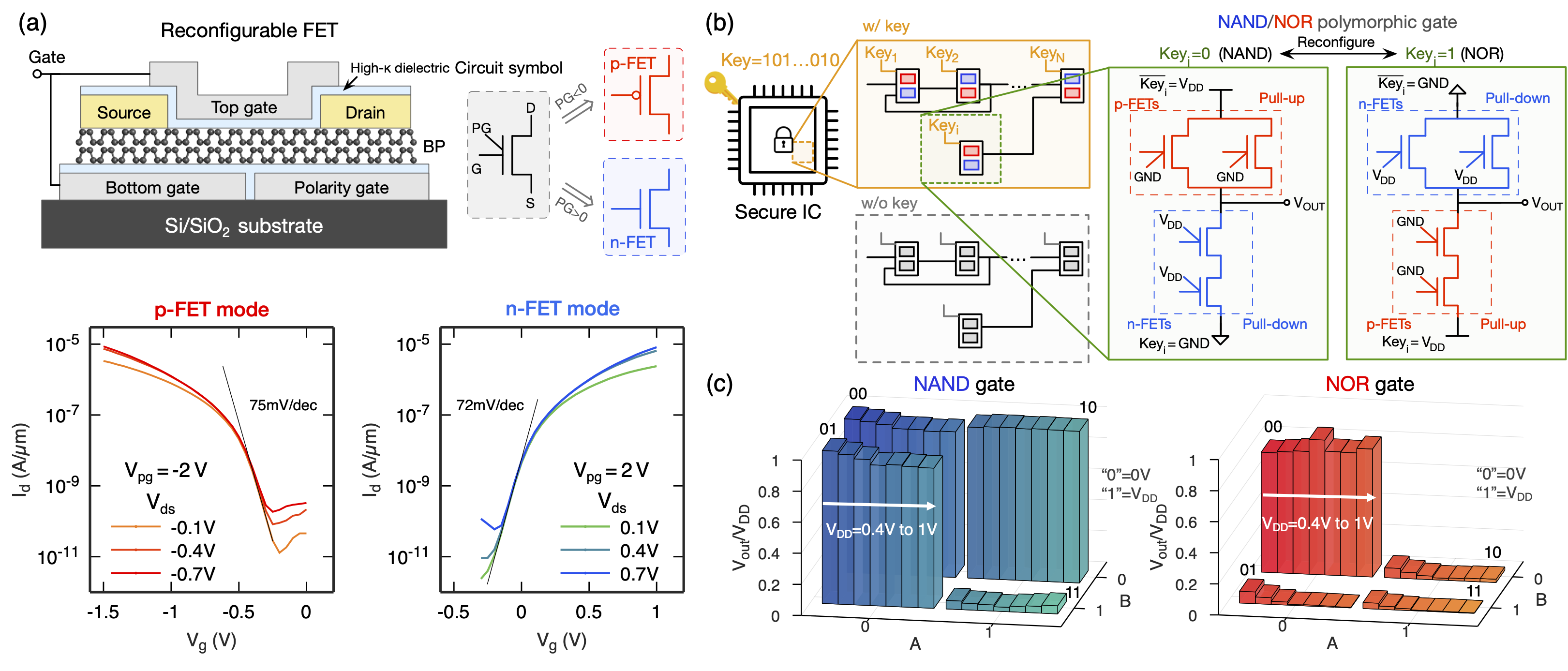

We developed a chip security scheme by leveraging the tunable polarity of 2D transistors. For traditional Si CMOS transistors, the polarities (p-type or n-type) are defined by substitutional doping in source/drain regions and cannot be altered after the chip is fabricated. By contrast, transistors based on 2D semiconductors rely on carrier injection through Schottky barriers at source/drain contacts and are inherently ambipolar, meaning both electron and hole injection are possible and can be tuned via gating. We demonstrated a reconfigurable FET (Fig. 1a) based on 2D material black phosphorus (BP) that can change into p-FET mode and n-FET mode by altering the bias on the polarity gate. Such tunable polarity can be used to implement polymorphic gate, a circuit whose functionality can be changed during runtime, which then can be used to build secure circuits that are resilient to reverse engineering (Fig. 1b). Since each polymorphic gate can provide two different functions, for a chip consisting of N polymorphic gates, attackers without the key bits would have to guess from 2N possibilities, even if they are able to map out all the circuit connections through reverse engineering (grey box in Fig. 1b). For large enough N, the exponential dependence ensures the extreme difficulty for attackers to decipher the circuit layout. Based on the reconfigurable 2D FETs, we have demonstrated an experimental NAND/NOR polymorphic gate (Fig. 1c), whose functionality can be changed from NAND gate and NOR gate by reversing the key bit, demonstrating a milestone of integrating 2D FETs into secure circuits.

Related publications:

-

2021

Nat. Electron.Nature Electronics, 4(1), 45–53, 2021

-

2019

APL Mat.APL Materials, 7(10), 100701, 2019