M.I.T. Laboratory for Computer Science

Network Implementation Note No. 26 April 24, 1980

V2.LNI Control Module Interface Specifications

by J. H. Saltzer and C. Ludwig

This note specifies the interface between the version two local network module, V2.LNI.CTL, and the host-specific buffer module, V2.LNI.HSB. As several versions of V2.LNI.HSB are being designed for the UNIBUS (V2.LNI.UNIBUS,) the nu-bus (V2.LNI.NU,) the S-100 bus (V2.LNI.S-100,) and the Q-bus (V2.LNI.Q,) errors, omissions, inconsistencies, and proposed revisions occur. To control the interface, this document separately identifies several different categories of information:

- 1. The agreed-upon interface specification. The meaning of agreed-upon is that all implementations either meet this specification or have a plan to evolve to it.

- 2. Proposed revisions to the specification, not yet agreed upon.

- Known differences between the agreed-upon specification and the various implementations and designs.

- 4. Questions that are not resolved by the specifications.

## Agreed-upon Ring Control Module Interface Specification

- The format of the data passed across the interface between V2.LNI.CTL and V2.LNI.HSB is the same as the V2.LNI 0.2 packet format. The order of bytes passed across this interface is the same as the order transmitted around the ring.

- Data is passed between V2.LNI.CTL and V2.LNI.HSB in 8-bit parallel form, one byte at a time. Data bit zero is placed on the ring first. (V2.LNI.HSB insures that data bit zero is the least significant bit of the character representation on the host.)

- 3. The length of the data packet is not passed explicitly; the end of the packet is signalled with separate status lines. This arrangement permits the entire V2.LNI.CTL to get along without data length counters.

- 4. Signals between the two modules (37 lines):

This note is an informal working paper of the M.I.T. Laboratory for Computer Science. It should not be reproduced without the author's permission, and it should not be cited in other publications. Set by HSB, read by CTL:

|        | Default |                                      |  |  |  |

|--------|---------|--------------------------------------|--|--|--|

| JOINR  | negate  | Join ring request                    |  |  |  |

| ENMOD  | negate  | Enable modem                         |  |  |  |

| INITR  | negate  | Initialize ring                      |  |  |  |

| ORIGR  | negate  | Originate request                    |  |  |  |

| ORST*  | negate  | Originate reset                      |  |  |  |

| COPYR  | negate  | Enable copy request                  |  |  |  |

| LBO    | assert  | Last byte out                        |  |  |  |

| OD0OD7 | negate  | Data out Bit numbered 0 is ASCII LSB |  |  |  |

| SGND   |         | Signal ground reference              |  |  |  |

Set by CTL, read by HSB:

| REFUS*  | assert | Originating packet refused           |  |  |

|---------|--------|--------------------------------------|--|--|

| RNOK*   | assert | Ring not circulating flags or tokens |  |  |

| JOIND   | negate | Node has joined ring                 |  |  |

| MESLOST | assert | Originating packet lost              |  |  |

| COPYC*  | negate | Copy operation complete              |  |  |

| ORIGC*  | negate | Originate operation complete         |  |  |

| ORGING  | negate | Originate operation in progress      |  |  |

| NBI*    | negate | Next byte in                         |  |  |

| NBO     | negate | Next byte out                        |  |  |

| LBI     | negate | Last byte in                         |  |  |

| BDFORM* | assert | Packet out of format                 |  |  |

| PERR*   | assert | Parity error                         |  |  |

| ID0ID7  | negate | Data in Bit numbered O is ASCII LSB  |  |  |

|         |        |                                      |  |  |

The sense of all lines is high-asserted. Asterisks in the above signal names identify those lines whose senses are inverted.

The "default" column specifies which direction the receiving end of the line should pull the line if the sending end of the line is neither asserting nor negating. This choice of default, together with the signal senses in the above list, is intended to guarantee that nothing untoward happens if the cable is accidentally disconnected. The intention is that the ring control module will do nothing, and the host-specific buffer module will return all possible error status to the host.

- 5. No explicit clock signals pass across the interface. To the extent possible, the interface is self-timed, with a line in one direction initiating some action and a return line that reports compliance. The exception is data transfer, which goes on at a rate determined by the ring transmission rate. The control module has an internal clock that it keeps synchronized with the ring data transmission rate; that clock provides pulses that are used to request transfer of data across the interface. For all lines, the timings relative to other lines are described in the following paragraphs and summarized in the next section.

- 6. The "originate request" line carries a level signal, asserted by the buffer module when it has a packet ready to originate. Data to be

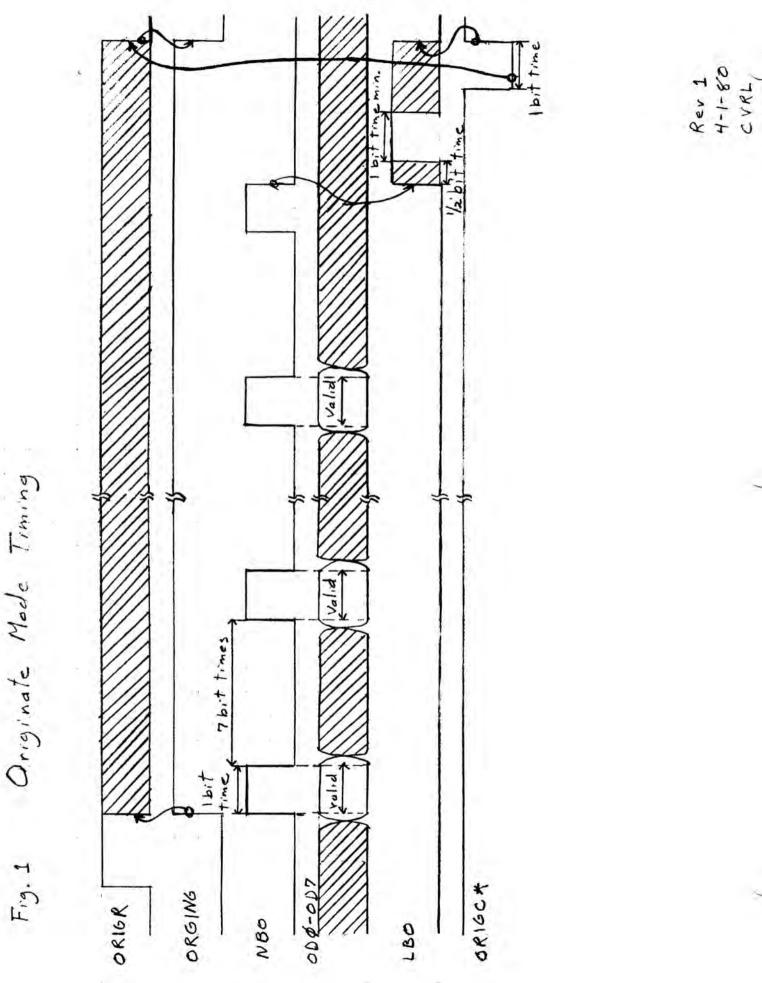

originated is transferred according to the following typical sequence (some steps can go on in parallel or in a different order; figure 1 and the summary of line timings specify the allowable range of such sequences):

- a) HSB asserts the "originate request" line.

- b) CTL detects a token, switches to originate mode, and asserts "originate operation in progress".

- c) HSB sets ODATA(0)...ODATA(7) and holds them constant until CTL negates "next byte out".

- d) CTL asserts "next byte out" for one bit time, then negates it.

- e) Steps c) and d) are repeated as many times as necessary to transfer all bytes. Step c) must be completed within 7 bit times after step d).

- f) HSB asserts "last byte out" simultaneously with ODATA(0)...ODATA(7), and negates it after CTL negates "next byte out".

- g) CTL transmits last byte and terminates packet.

- h) HSB negates the "originate request" line (unless it is prepared to send another packet.)

- i) CTL detects token/connector at end of originated packet.

- j) CTL asserts "originate operation complete" line for one bit time, then negates it.

- k) CTL negates "originate operation in progress".

The buffer module must negate its "originate request" line sometime before the control module negates "originate operation in progress," unless it is prepared to send another packet. If the "originate request" line remains asserted, V2.LNI.CTL will attempt to capture the token at the end of the packet just originated, and expect to send another packet. This design is intended to allow V2.LNI.CTL to be used with double buffered buffer modules for higher performance.

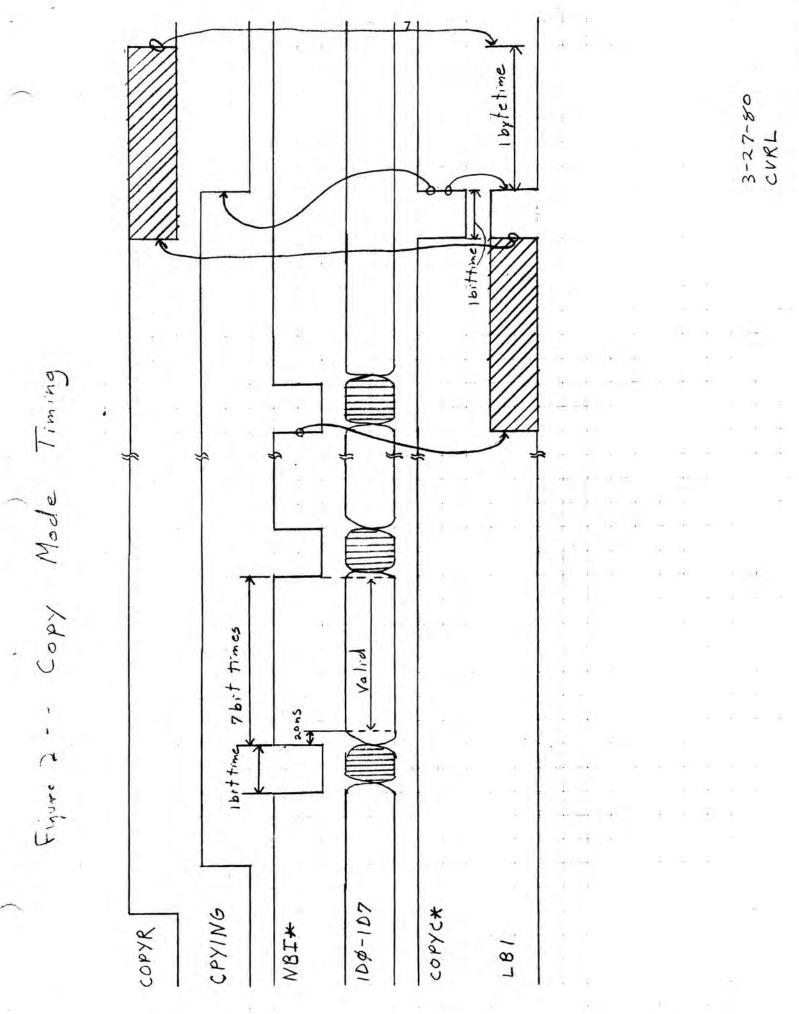

- 7. The "enable copy request" line carries a level signal, asserted by HSB when it is prepared to accept a received packet. If this level is asserted at the instant that CTL matches a packet destination address, CTL will begin to transfer data to HSB, according to the following sequence as illustrated in figure 2:

- a) HSB asserts the "enable copy request" line.

- b) CTL detects destination address match.

- c) CTL asserts "next byte in" for 1 bit time, then negates it. Data is available on IDATA(0)...IDATA(7) 20 ns. after negation of "next byte in". From the time that "next byte in" is negated HSB has seven bit times to read IDATA(0)...IDATA(7), before CTL goes on to step d).

- d) step c) is repeated as many times as necessary to transfer all bytes.

- e) CTL detects the end of packet signal.

- f) CTL asserts "last byte in".

- g) CTL asserts "copy operation complete" for 1 bit time, then negates it.

- h) HSB negates the "enable copy request" line, if it does not want another packet.

If either a packet format or link data error occurred during the packet copy operation, CTL will have asserted the corresponding status line for one bit time before it negates "copy complete". (The purpose of "last byte in" is to permit a CTL implementation to report the presence of the last byte before it has finished format and link data error checking. This early report in turn gives a double-buffered buffer module more time to decide whether or not it can immediately accept another packet.) The buffer module must negate the "enable copy request" line sometime after the "last byte in" signal comes from CTL, and before recognition of the destination address field of the next packet (At least one byte time and as much as 2.5 byte times if "last byte in" is signalled immediately upon detection of end of packet), unless it is prepared to accept two packets in a row. If it is so prepared, it has that interval before the first byte of the next packet arrives.

- 8. Negation of "originate operation in progress" occurs after the "originating packet refused" and "originating packet lost" status signals have been set and the link parity bit has been checked on the returned version of the just-originated packet. CTL sets "originating packet refused" and "originating packet lost" by asserting the corresponding line for one bit time.

- 9. The "link error" line is asserted by CTL for one bit time whenever a link parity error is noticed, independent of whether copying, origination, or just repeating is going on. The intent is that HSB either set a latch or bump a counter, either of which are readable and resettable by the host. When a packet has been copied or originated, the corresponding "in progress" signal is negated after link errors have been checked and, if necessary, signalled.

- 10. The "join ring" request line carries a level signal that is asserted by HSB to indicate that CTL should leave analog loop back mode and join the ring. When HSB negates the level, CTL should return to analog loop back mode.

- 11. The "enable modem" line carries a level signal that is asserted by HSB to indicate that CTL should leave digital loopback mode. It remains asserted as long as that mode of operation is required. Both "enable modem" and "join ring" must be asserted in order to participate in the ring.

- 12. The "node has joined ring" line carries a level signal that CTL asserts whenever it detects current flowing in the relay control line. CTL negates this level if current stops flowing.

- 13. For the 8.3 Mhz V2.LNI.CTL, a bit time may range from 100 to 140 ns.

## Summary of line timings

2.314

|               | [ T                                                           |                                        | 1                                 |                                                                                            |

|---------------|---------------------------------------------------------------|----------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------|

|               | earliest<br>allowable<br>assertion<br>is after                | latest<br>allowable<br>assertion       | earliest<br>allowable<br>negation | time                                                                                       |

| JOINR         | ENMOD<br>asserted (?)                                         | is before ?                            | is after ?                        | is before<br>?                                                                             |

| ENMOD         | power up (?)                                                  | no limit                               | JOINR negated                     | power down (?)                                                                             |

| ORIGR         | first byte<br>available<br>to transfer                        | no limit                               | ORGING<br>asserted                | ORGING negated<br>(unless another<br>packet is ready<br>to transfer)                       |

| ORST          | ORGING<br>asserted                                            | no limit                               | l bit time<br>after<br>assertion  | ORIGR negated                                                                              |

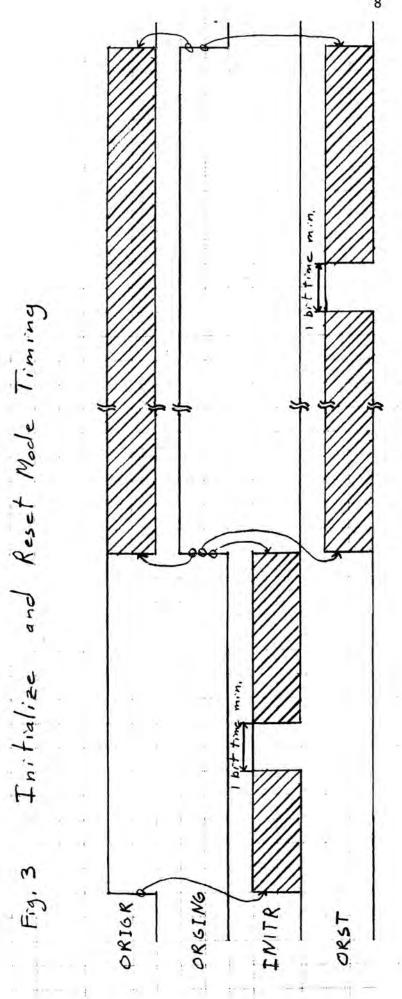

| INITR         | ORIGR<br>and RNOK*<br>asserted                                | ORGING<br>asserted                     | l bit time<br>after<br>assertion  | ORIGR negated                                                                              |

| COPYR*        | prepared to<br>accept data                                    | first bit of<br>address is<br>received | LBI asserted                      | COPYC* negated<br>+ 1 byte time<br>(unless HSB<br>prepared to<br>accept another<br>packet) |

| LBO           | second<br>negation of<br>NBO after<br>last valid<br>data byte | negation of<br>NBO + ½ bit<br>time     | l bit time<br>after<br>assertion  | ORGING negated                                                                             |

| first<br>ODO7 | no limit                                                      | ORIGR asserted                         | negation of<br>NBO                | negation of NBO<br>+ 7 bit times                                                           |

| later<br>0D07 | negation of<br>NBO                                            | negation of<br>NBO + 7 bit<br>times    | next negation<br>of NBO           | next negation<br>of NBO + 7<br>bit times                                                   |

| REFUS*        | ORIGR<br>asserted                                             | (pulse asserted                        | for 1 bit time)                   | ORGING negated                                                                             |

| RNOK*         | no token<br>detected for<br>300 ms or no<br>flag detected     | ?                                      | token or flag<br>detected         | ?                                                                                          |

|               | for 1.5 ms                                                    |                                        |                                   | continued on next pag                                                                      |

9

continued on next page

| -                          |                                            |                     | j                                             |                                           |

|----------------------------|--------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------|

|                            | 1                                          |                     | 1                                             | time-                                     |

|                            | earliest                                   | latest              | earliest                                      | latest                                    |

|                            | allowable                                  | allowable           | allowable                                     | allowable                                 |

|                            | assertion                                  | assertion           | negation                                      | negation                                  |

|                            | is after                                   | is before           | is after                                      | is before                                 |

| JOIND relay current no lin |                                            | no limit            | no limit                                      | relay current                             |

|                            | flow detected                              |                     |                                               | stops flowing                             |

| MESLOST                    | ORIGR<br>asserted                          | (Pulse asserted     | for 1 bit time)                               | ORGING negated                            |

| COPYC*                     | 7 bit times<br>after last NBI*<br>negation | same as<br>earliest | (Pulse asserted                               | for 1 bit time)                           |

| ORIGC*                     | 9 bit times<br>after last NBO<br>negation  | same as<br>earliest | (Pulse asserted                               | for 1 bit time)                           |

| ORGING                     | ORIGR<br>asserted                          | no limit            | 8 bit times<br>after last<br>NBI*<br>negation | same as<br>earliest                       |

| first<br>NBI*              | COPYR<br>asserted + 7<br>bit times (?)     | ?                   | (Pulse asserted                               | for 1 bit time)                           |

| later<br>NBI*              | 7 bit times<br>after last<br>NBO negate    | same as<br>earliest | (Pulse asserted                               | for 1 bit time)                           |

| first<br>NBO               | ORGING<br>asserted (?)                     | ?                   | (Pulse asserted                               | for 1 bit time)                           |

| later<br>NBO               | 7 bit times<br>after last<br>NBO negate    | same as<br>earliest | (Pulse asserted                               | for 1 bit time)                           |

| LBI                        | last NBI<br>asserted                       | (Pulse asserted     | for 1 bit time)                               | COPYC*<br>negated                         |

| BDFORM*                    | ?                                          | ?                   | ?                                             | ?                                         |

| PERR                       | (Pulse asserted<br>time)                   | for 1 bit           | same as<br>latest                             | 9 bit times<br>after last NBO<br>negation |

| IDO ID7                    | NBI*                                       | NBI*                | NBI* asserted                                 | NBI* negated                              |

|                            | asserted                                   | negated             | + 7 bit                                       | + 7 bit                                   |

|                            |                                            |                     | times                                         | times                                     |

10

1.1

.

## Proposed Changes to interface specifications

- Originate and copy protocols could be made more symmetric, two lines of the specified interface eliminated, and the originate protocol simplified, with the following change:

- a) eliminate the HSB-originated pulse signal LBO.

- b) use negation of ORIGR in response to some NBO pulse as a signal that the last byte has already been transmitted. A double-buffered HSB could re-assert ORIGR for the next packet anytime after that NBO is completed and before CTL negates ORGING.

For symmetry, on the copy side, the current V2.LNI.UNIBUS implementation (which already omits LBI, using COPYC\* instead) would be made standard, and the LBI line eliminated from the specification.

- The three lines ORIGC\*, COPYC\*, and ORGING could be condensed to two, a timing-dependent specification eliminated, and the originate and copy protocols made symmetric by the following change:

- Add a line "copy operation in progress," or CPYING, which is specified as follows:

| CPYING | COPYR*   | 7 bit times  | 10 bit times   | same as  |

|--------|----------|--------------|----------------|----------|

|        | asserted | before first | after last NBO | earliest |

|        |          | NBI*         | negation       |          |

- b) Eliminate ORIGC\* and COPYC\*. All HSB circuits that use them would respond instead to negation of ORGING and CPYING, respectively.

- c) Revise the specifications of COPYR\* and LBI to refer to CPYING rather than COPYC\*.

Known Differences between specification and V2.LNI.CTL--V2.LNI.UNIBUS Implementation:

- 1. JOINR, ENMOD, and NIR lines are implemented, but do not do anything yet.

- LBI is not provided (HSB is using COPYC\* for this purpose. Note that originate and copy are thereby more asymmetric protocols than necessary.)

- An extra line, "card enable", is implemented. CTL will not operate unless card enable is held at ground level. CTL pulls this line high if it is neither asserted nor negated.

- The CPYING line is implemented as proposed above. However, V2.LNI.UNIBUS still makes use of ORIGC\* and COPYC\*.

Questions

- 1. The timing when BDFORM\* is meaningful has not been specified.

- 2. The timing limits of the first NBI and NBO have not been specified.

- 3. Timing requirements on RNOK\* have not been completely specified.

- 4. The latest timing limit on ORIGR negation may be too late to permit CTL to recapture the just-originated token. This problem would prevent implementation of a double-buffered HSB. It may be necessary to specify ORIGR negation no later than LBO assertion, or perhaps one-byte time thereafter.

- 5. The specified timing limits on JOINR and ENMOD are questionable.

- 6. INITR, ORST, and LBO, which are set by HSB, are specified as pulses of minimum width one bit time, but HSB does not have any clock that allows it to measure a bit time. It may be necessary to change these to a self-timed protocol.

- 7. The earliest possible assertion of LBO may be misspecified. The present CTL implementation seems to allow an earlier assertion.

- 8. The proper sequence for INITR and ORIGR is in dispute; the question revolves around whether or not RNOK\* assertion causes ORIGR to be dropped, an issue in the interface between HSB and the programmer.

- 9. The operation of CTL is not specified if either ORIGR or COPYR is dropped prematurely. Some specification may be appropriate.

1.2